INTERNAL SPECIFICATIONS

59

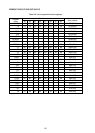

4.2.2 Internal data memory registers R0 thru R7

Four banks of registers group exist in the data memory (RAM) between memory addresses

00 thru 1FH. Banks are specified by RS0 and RS1 bit combinations within the program status

word (PSW). Note that the register area R0 thru R7 can also be used as normal data memory.

The PSW table is shown in Table 4-1, and the data memory register bank layout in Figure 4-

3.

Table 4-1 Program status word (PSW)

Bit 76543210

Flag CY AC F0 RS1 RS0 OV F1 P

Set • •

00 0 D7 D6 D5 D4 D3 D2 D1 D0 R0

01 1 D7 D6 D5 D4 D3 D2 D1 D0 R1

02 2 D7 D6 D5 D4 D3 D2 D1 D0 R2

03 3 D7 D6 D5 D4 D3 D2 D1 D0 R3

04 4 D7 D6 D5 D4 D3 D2 D1 D0 R4

05 5 D7 D6 D5 D4 D3 D2 D1 D0 R5

06 6 D7 D6 D5 D4 D3 D2 D1 D0 R6

07 7 D7 D6 D5 D4 D3 D2 D1 D0 R7

08 8 D7 D6 D5 D4 D3 D2 D1 D0 R0

0F 15 D7 D6 D5 D4 D3 D2 D1 D0 R7

10 16 D7 D6 D5 D4 D3 D2 D1 D0 R0

17 23 D7 D6 D5 D4 D3 D2 D1 D0 R7

18 24 D7 D6 D5 D4 D3 D2 D1 D0 R0

1F 31 D7 D6 D5 D4 D3 D2 D1 D0 R7

20 32 D7 D6 D5 D4 D3 D2 D1 D0

2F 47 D7 D6 D5 D4 D3 D2 D1 D0

30 48 D7 D6 D5 D4 D3 D2 D1 D0

OFF

255 D7 D6 D5 D4 D3 D2 D1 D0

STACK & DATA RAM

USER DATA RAM

BIT ADDRESSING

BANK 3

BANK 2

BANK 1

BANK 0

1

1

0

0

1

0

1

0

RS1 RS0

Figure 4-3 Internal data memory register bank layout