MSM80C154S/83C154S/85C154HVS

136

4.7.4 Detection of external interrupt signals INT0 and INT1

4.7.4.1 Outline of INT signal detection

Detect modes of the external interrupt signals 0 and 1 can be set to level-detect or trigger-

detect mode by the IT0 and IT1 data values in the timer control register (TCON 88H) as

indicated in Table 4-22.

Table 4-22 TCON[88H] register

76543210

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

Bit

Flag

••Set

Timer INT1 INT0

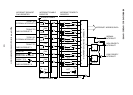

4.7.4.2 External interrupt signal 0 and 1 level detection

When bit 0 (IT0) in the timer control register (TCON 88H) is “0”, external interrupt 0 is level-

activated. And when bit 2 (IT1) is “0”, external interrupt 1 is also level-activated. With the

external interrupt signals in level-detect mode, external interrupts 0 and 1 are level-detected

by the equivalent circuit shown in Figure 4-47.

When the level of the external interrupt pin is “0” at S5 timing, the level is latched and the Q

output becomes “1”. The latched external interrupt signal is set as the external interrupt flag

in the timer control register (TCON) at S3 timing. The interrupt flag set by external interrupt

signal is always reset at S6 timing of the end of the machine cycle, thereby executing the

equivalent of a “level sense” operation. The cycle width of the respective “0” and “1” levels

of the external interrupt signal applied to the external interrupt pin in this case must be at least

12 times (12T) the XTAL1·2 oscillator clock cycle time T.

And the external interrupt signal should be held at “0” level until the corresponding interrupt

is actually generated.

S3

QS

R

RESET

1

0

12T 12T 12T

QD

L

S5

INT

0 or

INT

1

S6

MEND

IE0 or 1

Figure 4-47 Interrupt level detect equivalent circuit for IT bit “0”