INPUT/OUTPUT PORTS

201

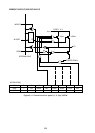

5.4 Port 2

Port 2 can function as a quasi-bidirectional port capable of handling input and output of 8-bit

data in the circuit configuration outlined in Figure 5-8. It can also be used for output of

addresses 8 thru 15 in external ROM and external RAM (using DPTR) modes. When port 2

is used as a quasi-bidirectional port, it functions in much the same way as port 1. Note,

however, that the port 2 “1” data accelerator circuit operates for a period equivalent to four

XTAL1·2 oscillator clocks.

Output of addresses 8 thru 15 obtained from port 2 is activated by the circuit outlined in Figure

5-9. When the address output data is “1”, the “1” data accelerator circuit is activated during

output of the data, resulting in a higher driving capacity.

To change port 2 from a quasi-bidirectional input port to a high impedance input port, “1” is

set in bit 2 (P2HZ) of the I/O control register (IOCON 0F8H). The output driver circuit is thus

disconnected from the port pin and the port becomes a high impedance input port. The signal

levels applied to high impedance input ports are normal “0” and “1” level signals. The pins

cannot be used in open status.

When port outputs are floated in CPU power down mode (PD, HPD), the port 2 pins may be

either open, or undefined within the –0.5 to VCC+0.5V range. The port 2 pin table is given in

Table 5-4.

Q

D

READ

INTERNAL

BUS

WP2

Q

D

C

PC/DATA

P1

VCC

P2 P3

PORT 2

N

Q

MODIFY

CONTROL

PC8~15

RA8~15

(DPH)

Figure 5-8 Port 2 internal equivalent circuit