MSM80C154S/83C154S/85C154HVS

120

B = fOSC ×

65536-DRCAP2

1

×

16

1

2

1

×

where B is the baud rate, fOSC the fundamental oscillator (XTAL1·2) frequency, and DRCAP2

the contents of RCAP2L and RCAP2H (expressed in decimal).

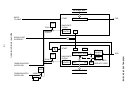

4.6.3.4.3 Mode 3 transmit operation

The transmit basic clock (TXCLOCK in Figure 4-36) is obtained from a hexadecimal free-run

counter overflow where timer/counter 1 or timer/counter 2 overflow is used as the clock.

Transmission is commenced when transmit data is written in SBUF.

The start bit, the eight SBUF data bits (with the LSB first), TB8, and the stop bit are transmitted

sequentially from the TXD synchronized with the basic clock.

As soon as the TB8 output has been completed, the transmit circuit is initialized, and the T1

flag is set at the first M1·S3 after the completion of that output.

4.6.3.4.4 Mode 3 receive operation

The receive circuit timing is generated by a hexadecimal counter overflow where timer/

counter 1 or timer/counter 2 overflow is used as the clock, and the input data received from

the RXD is bit synchronized. That is, at the same time that reception is started following input

of the start bit, the hexadecimal counter commences to count up, and with one complete

round of the hexadecimal counter corresponding to one bit of received data, reception is

continued by the receive circuit. Therefore, timer/counter 1 must be set so that the period of

a single round of the hexadecimal counter is equal to the reception data baud rate.

The RXD change from “1” to “0” is regarded as the beginning of the start bit where reception

is commenced.

When this “1” to “0” RXD change is detected, the hexadecimal counter which had been

stopped in reset status commences to count up. When the hexadecimal counter is in state

7, 8, and 9, the start bit is sampled, and is accepted as valid if at least two of the three sampled

values are “0”, thereby enabling data reception to continue. If two or three of the sampled

values are “1”, the start bit becomes invalid, and the receive circuit is initialized when the

hexadecimal counter reaches state 10.

The reception data is sampled when the hexadecimal counter is in state 7, 8, and 9, and the

more common value of the three sampled values is read sequentially as data into the input

shift register.

If the hexadecimal counter is in state 10 during the period of the next bit (that is, the multi-

purpose data bit) after the eight bits of data have been received, and if the conditions stated

below are satisfied, the input shift register data (the LSB being read first) is loaded into SBUF,

and the sampled multi-purpose data bit is read into RB8. And when the hexadecimal counter

is in state 10 during the period of the next after that (that is, the stop bit) the receive circuit

is initialized.

The RI flag is set at the first M1·S3 after that.

Conditions: (1) RI=“0”

(2) SM2=“0”, or SM2=“1” and sampled multi-purpose data bit=“1”