INTERNAL SPECIFICATIONS

93

EXF2 : Timer/counter 2 external flag bit which is set when the T2EX pin level (bit 1 of

port 1) is changed from “1” to “0” at EXEN2=1. This flag serves as the timer

interrupt 2 request signal. When an interrupt is generated, this flag must be reset

to “0” by software.

TF2 : Timer/counter 2 internal flag bit which is set when a carry signal is generated by

timer/counter 2 in 16-bit auto reload mode or capture mode. This flag serves as

the timer interrupt 2 request signal. When an interrupt is generated, this flag

must be reset to “0” by software.

4.5.3.3 Timer/counter 2 operation modes

Timer/counter 2 operation modes are set by combinations of the CP/RL2, TCLK, and RCLK

bits in timer 2 control register (T2CON 0C8H) shown in Table 4-13. The timer modes are listed

in Table 4-14.

Table 4-13 Timer 2 control register (T2CON 0C8H)

Bit

Flag

Set

76543210

TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2 CP/RL2

•• •

Table 4-14 Timer/counter 2 modes

RCLK TCLK CP/ RL2 TR2

0001

0011

RCLK + TCLK = 1 × 1

×××0

Mode

16-bit auto reload

16-bit capture

Baud rate generator

All operations stopped

4.5.3.3.1 16-bit auto reload mode

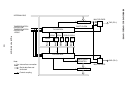

16-bit auto reload mode is set by making the circuit connection shown in Figure 4-20 by setting

RCLK=0, TCLK=0, and CP/RL2=0 as the bit conditions in timer 2 control register (T2CON).

Timer/counter 2 operates in the following way when 16-bit auto reload mode is set. When a

timer/counter 2 carry signal is generated, or when the signal applied to the T2EX pin (bit 1

of port 1) is changed from level “1” to “0”, the reload data in the RCAP2L and RCAP2H

registers is preset in L2 and TH2 of timer/counter 2. The timer/counter thus starts counting

from this preset value.

The timer/counter 2 carry signal is set in internal timer flag 2 (TF2), and the T2EX change is

set in external timer flag 2 (EXF2). The TF2 and EXF2 serve as the timer interrupt 2 request

signals with an interrupt call being made to address 43 (2BH) if the timer interrupt 2 has been

enabled. If an interrupt routine is commenced, the TF2 and EXF2 flags must be reset to “0”

by software.