MSM80C154S/83C154S/85C154HVS

104

4.6.2.5 SMOD

SMOD controls the division of the baud rate clock source when the serial port is in UART mode

(mode 1, 2, or 3).

If SMOD is cleared when in mode 1 or 3, the timer/counter 1 overflow frequency divided by

2 becomes the baud rate clock source. And if SMOD is set, the timer/counter 1 overflow

becomes the baud rate clock source.

When TCLK is set in mode 1 or 3, however, and timer/counter 2 is the baud rate clock source

for the transmitting circuit, SMOD has no effect on the transmitting baud rate. And if RCLK

has been set, timer/counter 2 becomes the baud rate source for the receiving circuit, and

SMOD has no effect on the receiving baud rate.

If SMOD is cleared in mode 2, 1/2 OSC (oscillator frequency divided by 2) divided by 2

becomes the baud rate clock source. And if SMOD is set, 1/2 OSC becomes the baud rate

clock source.

SMOD is located at bit 7 of PCON (power control register) specified by data address 87H.

Designation by bit address is not possible.

See Table 4-17 for the corresponding baud rate clock sources for TCLK, RCLK, and SMOD.

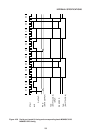

Table 4-17 Corresponding baud rate clock sources for TCLK, RCLK, and SMOD

Mode TCLK or RCLK SMOD Baud rate colck source

0 X X MSM83C154S fundamental timing

0 0 T/C1 overflow divided by 2

1 0 1 T/C1 overflow

1 X T/C2 overflow

2

X 0 1/2 OSC divided by 2

X 1 1/2 OSC

0 0 T/C1 overflow divided by 2

3 0 1 T/C1 overflow

1

Note: X

T/C1

T/C2

1/2 OSC

: Don't care

: Timer/counter1

: Timer/counter2

: Oscillator frequency (XTAL1•2) divided by 2

X T/C2 overflow