T1/E1/J1 Framer Initialization

76 Interphase Corporation

Multiplexed Direct Mode

In multiplex direct mode, the four framers have the same rhythm. SWMODE_N = 1 and

COMCLK_N = 1.

System Interface

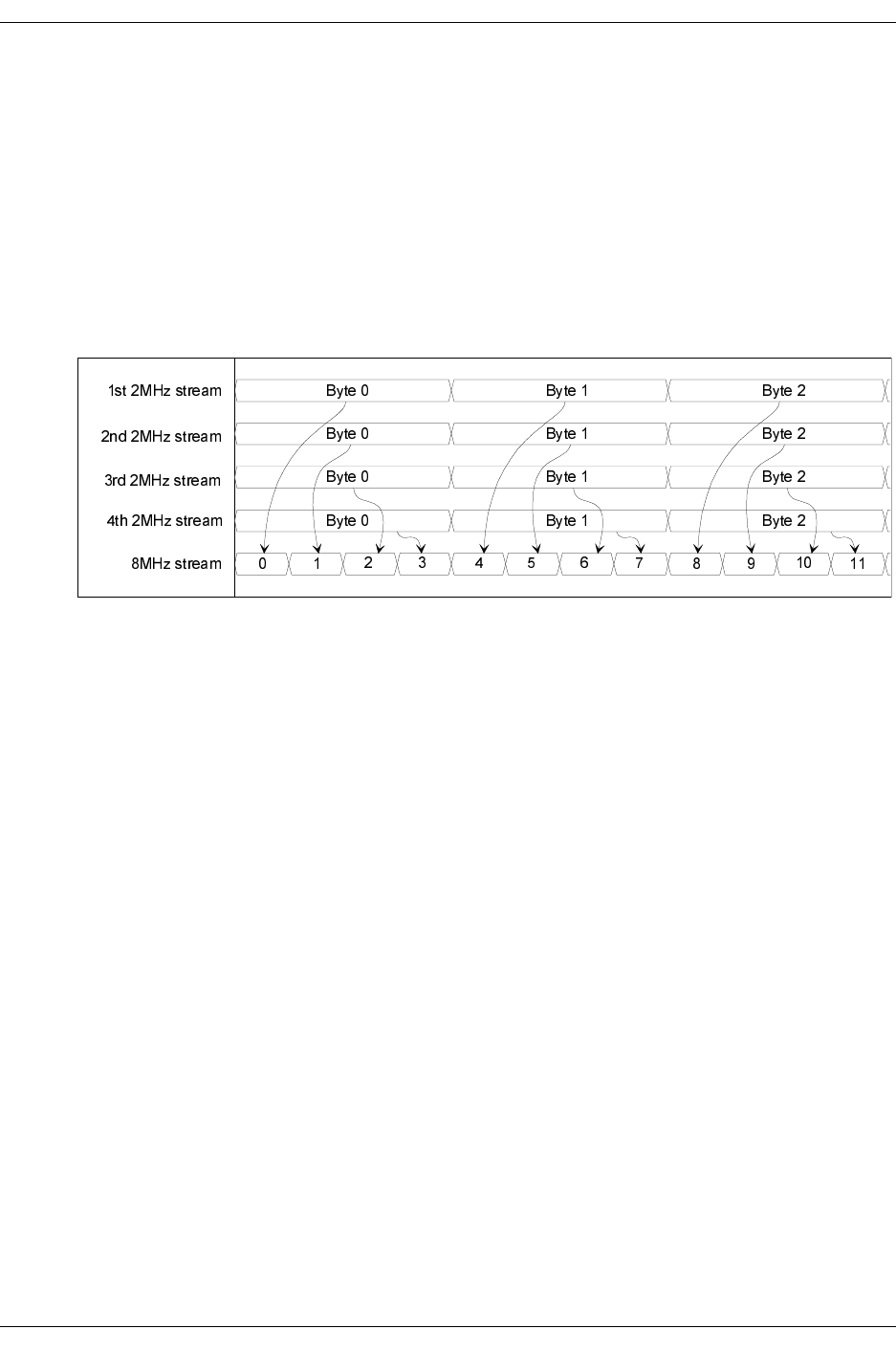

QuadFALC is connected to the CPM through an 8 MHz stream. This stream is the

concatenation of four 2 MHz streams, corresponding to the four T1/E1/J1 lines. These four

streams are mapped into this 8 MHz stream in an interleaved manner.

This interleaved organization is extended to all the 8 MHz streams.

Figure 3-1. Mapping of Four 2 MHz Streams into an 8 MHz Stream

See Boot Firmware sources: tst\c\qfalc.c - Functions gvQFalcInitT1, gvQFalcInitJ1 and

gvQFalcInitE1.

On the QuadFALC, the system multiplex mode must be enabled (GPC1.SMM = 1) with

byte interleaved format (SIC1.BIM=0), clocking rate at 8.192 MHz ( SIC1.SCC1/0=10)

and data rate at 8.192 MBit/s (SIC1.SDD1=1, FMR1.SDD0=0). Time-slot offset

programming was obtained by actual practice: XC0 = 0x00, XC1 = 0x03, RC0 = 0x00, RC1

= 0x03. The receive buffer size must be set to two frames (SIC1.RBS1/0 = 00). The transmit

buffer size must be set to two frames (SIC1.XBS1/0 = 10). SIC3.RESX and SIC3.RESR

must be set to 0 (Synchronous Pulse Transmit (–SYPX) and Synchronous Pulse Receive

(–SYPR) are latched on first clock (8.192 MHz) rising edge). –SYPX and –SYPR inputs

are mapped to XPA1 and RPA1 pins respectively by setting the PC1 register to 0.

SCLKX_1 and SCLKR_1 must be configured as inputs by setting PC5.CSXP and

PC5.CSRP bits to 0. All these initializations must be performed on each channel.

The multiplexed data stream is internally logically ored. Therefore the selection of the

active channel phase has to be configured differently for each single channel (1–4).

Programming is done with SIC2.SICS2...0 bit as shown in Table 3-2.