Chapter 1: Hardware Description

4538 Hardware Reference Manual 7

NOTE

Accesses from the CPM and the PowerSpan cannot go through the Memory

Management Unit (MMU), unlike the core accesses. Therefore, the CPM and

PowerSpan must use the physical addresses when accessing the SDRAMs (most

significant bit = 0). Accesses to 0x8000 0000 will not address the SDRAMs.

Interrupts

The PCI bridge PowerSpan and the communication peripherals generate interrupt requests

to the PowerQUICC II. These interrupts are level sensitive, active low.

Memory Controllers

The sophisticated memory controller units included in the PowerQUICC II are used on the

4538 boards to control all the external devices, except the PowerSpan, which is directly a

60x bus-compatible device. These units are a General Purpose Chip-select Machine

(GPCM) for SRAM, FLASH, and peripherals control, three User Programmable Machines

(UPM), and two SDRAM control machines (one used for Main SDRAM on 4538).

The memory controller unit to be used is defined bank per bank. Each bank is defined by

its Base Register (BRx) and its Option Register (ORx). The memory machine selection is

done in the Option register.

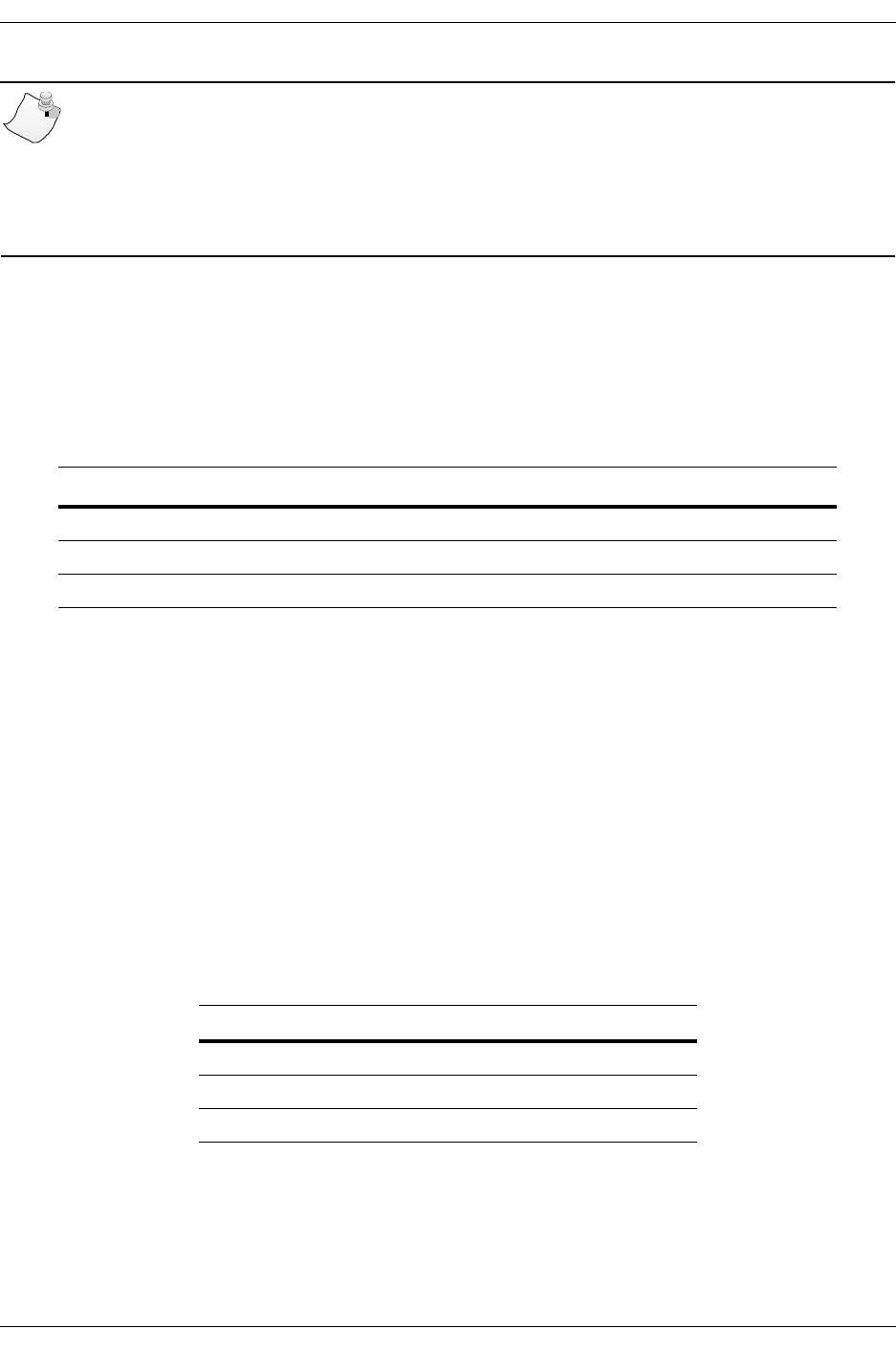

Table 1-2. Local Interrupts

Source MPC2860 Pin MPC8260 IRQ

3RZHU6SDQLQWHUUXSW$71 ±,54'3±(;7B%* ±,54

4XDG)$/&,QWHUUXSW

±,54'3±7/%,6<1&±(;7B'%* ±,54

(WKHUQHW/,8/;7$LQWHUUXSW

±,54'3±&.673B287±(;7B%5 ±,54

Table 1-3. PowerQUICC II Memory Controller Machine Usage

Element Accessed Bank Memory Controller

)/$6+((3520

[EXV*3&0

[EXV0DLQPHPRU\

[EXV6'5$0PDFKLQH

4XDG)$/&

[EXV830$