ISP Enable Jumper JP1

106 Interphase Corporation

WARNING

J5 Debug Connector is not compliant to PMC component height specification. It

should be removed to insert the 4538 and its carrier into a CompactPCI chassis.

ISP Enable Jumper JP1

The 4538 includes a location for a jumper at JP1. This location is used during production

to enable the programming of the card’s EPLD programmable devices “in-situ”. This

location should never be used by the normal user.

Blank Card Jumper JP2

Location for a jumper at JP2 is needed for production when the PowerSPAN serial

EEPROM is not yet programmed, in order to prevent the card from locking the system. This

location should never be populated with a jumper by the normal user.

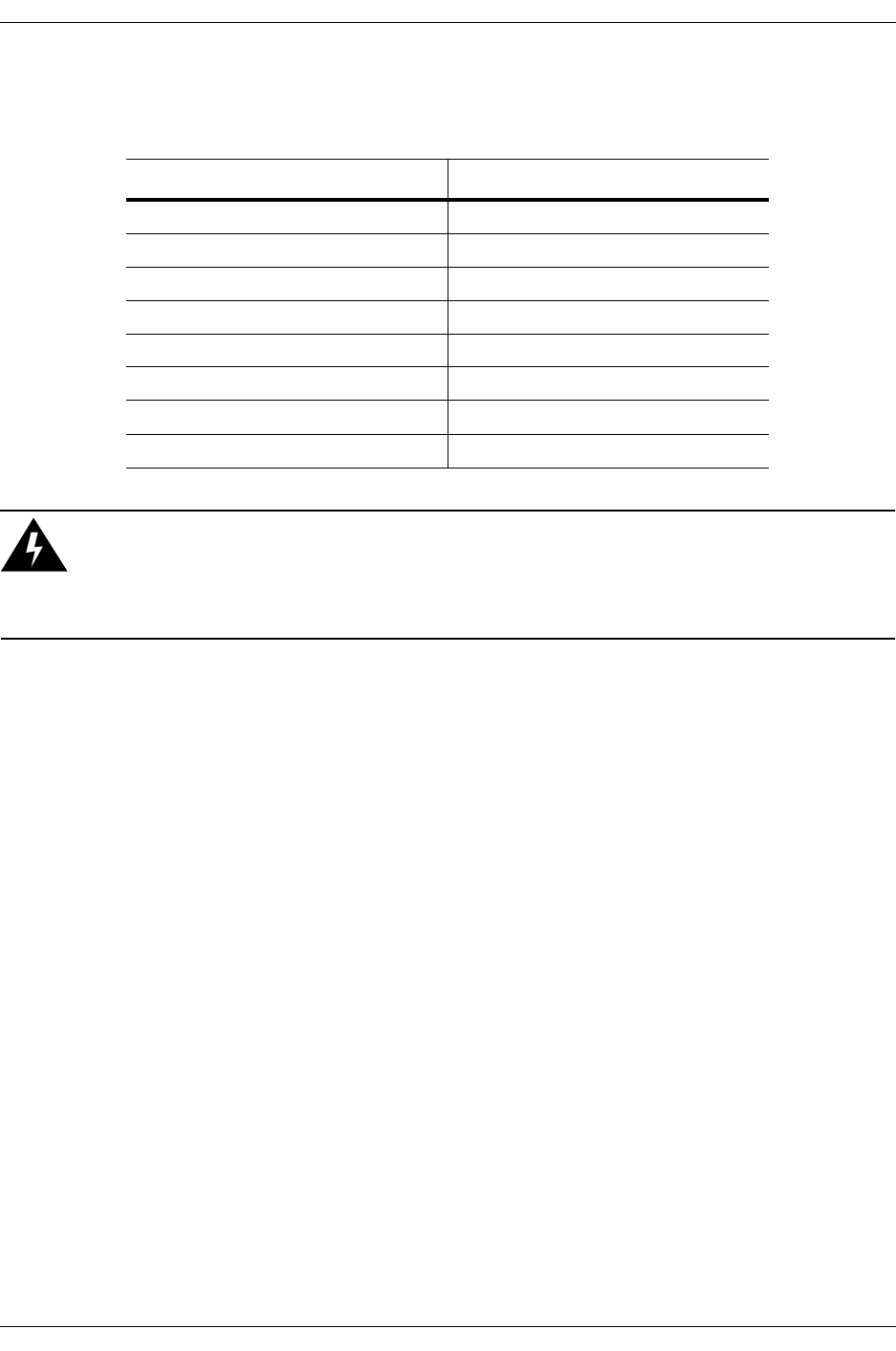

Table 5-7. J5 Debug Port

Pin Signal Signal Pin

1TDO 10 k

W Pull-up to +3.3 V 2

3TDI TRST_N4

5 QREQ_N +3.3V through a 1 kW resistor 6

7TCK 8

9TMS 10

11 SRESET_N GND 12

13 HRESET_N 14

15 10 k

W Pull-up to +3.3 V GND 16