The PCI Bridge

16 Interphase Corporation

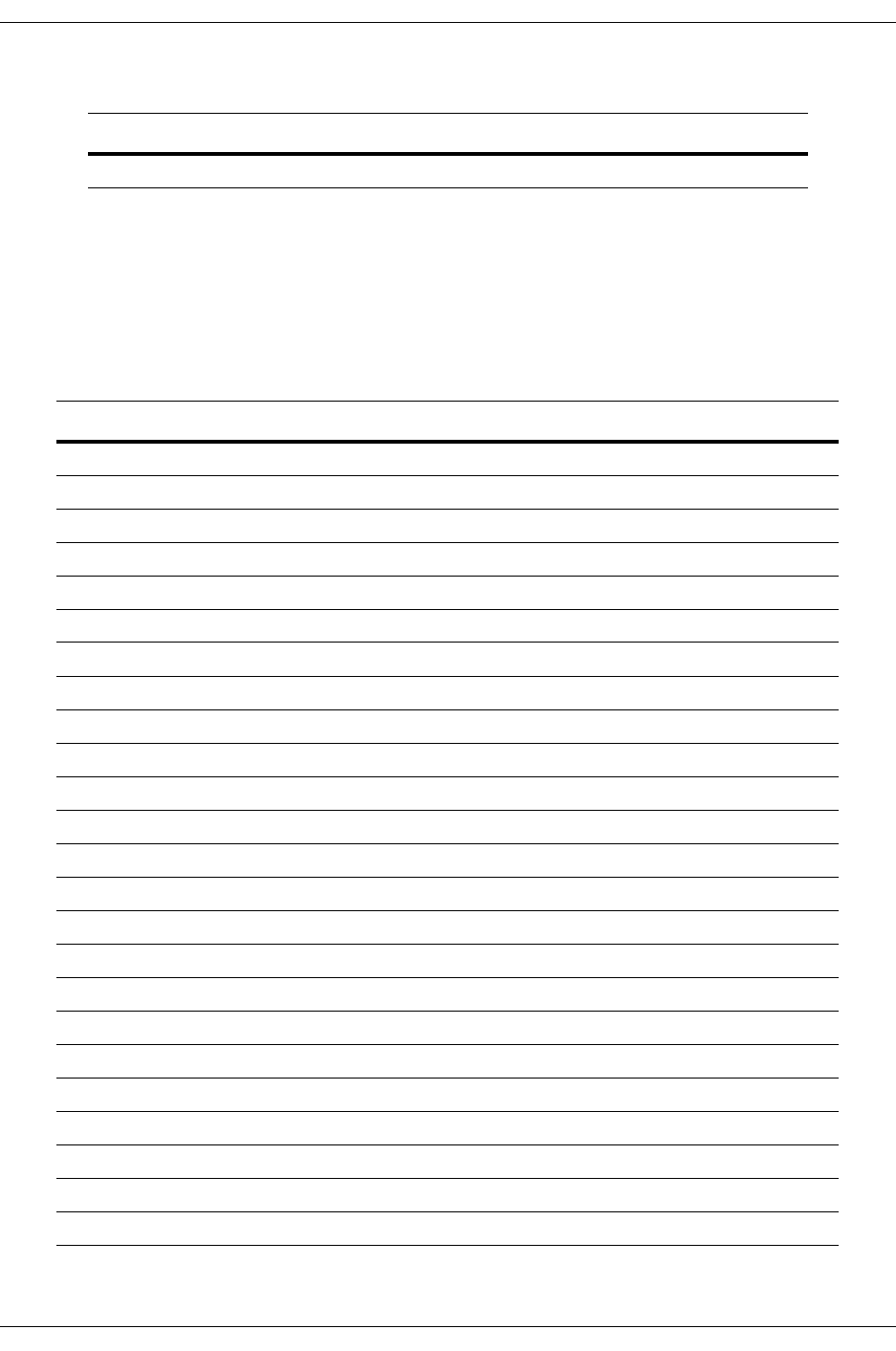

PowerSpan Processor Bus Registers

These registers are used to define the parameters of the local to PCI windows. They are

mapped in the PCI memory space (base address defined in PCI configuration register 0x14

PCIBAR1) and in the local space for the local processor (base address 0xF0020000).

[ 3B$5%B&75/ 3&,%XV$UELWHU&RQWURO5HJLVWHU

Table 1-17. PowerSpan Processor Bus Registers

Offset Register Description

[ 3%B6,B&7/ 3URFHVVRU%XV6ODYH,PDJH&RQWURO5HJLVWHU

[ 3%B6,B7$''5 3URFHVVRU%XV6ODYH,PDJH7UDQVODWLRQ$GGUHVV5HJLVWHU

[ 3%B6,B%$''5 3URFHVVRU%XV6ODYH,PDJH%DVH$GGUHVV5HJLVWHU

[ 3%B6,B&7/ 3URFHVVRU%XV6ODYH,PDJH&RQWURO5HJLVWHU

[ 3%B6,B7$''5 3URFHVVRU%XV6ODYH,PDJH7UDQVODWLRQ$GGUHVV5HJLVWHU

[ 3%B6,B%$''5 3URFHVVRU%XV6ODYH,PDJH%DVH$GGUHVV5HJLVWHU

[ 3%B6,B&7/ 3URFHVVRU%XV6ODYH,PDJH&RQWURO5HJLVWHU

[ 3%B6,B7$''5 3URFHVVRU%XV6ODYH,PDJH7UDQVODWLRQ$GGUHVV5HJLVWHU

[ 3%B6,B%$''5 3URFHVVRU%XV6ODYH,PDJH%DVH$GGUHVV5HJLVWHU

[ 3%B6,B&7/ 3URFHVVRU%XV6ODYH,PDJH&RQWURO5HJLVWHU

[ 3%B6,B7$''5 3URFHVVRU%XV6ODYH,PDJH7UDQVODWLRQ$GGUHVV5HJLVWHU

[ 3%B6,B%$''5 3URFHVVRU%XV6ODYH,PDJH%DVH$GGUHVV5HJLVWHU

[ 3%B6,B&7/ 3URFHVVRU%XV6ODYH,PDJH&RQWURO5HJLVWHU

[ 3%B6,B7$''5 3URFHVVRU%XV6ODYH,PDJH7UDQVODWLRQ$GGUHVV5HJLVWHU

[ 3%B6,B%$''5 3URFHVVRU%XV6ODYH,PDJH%DVH$GGUHVV5HJLVWHU

[ 3%B5(*B%$''5 3URFHVVRU%XV5HJLVWHU,PDJH%DVH$GGUHVV5HJLVWHU

[ 3%B&21)B,1)2 3URFHVVRU%XV3&,&RQILJXUDWLRQ&\FOH,QIRUPDWLRQ5HJLVWHU

[ 3%B&21)B'$7$ 3URFHVVRU%XV3&,&RQILJXUDWLRQ&\FOH'DWD5HJLVWHU

[$ 3%B3B,$&. 3URFHVVRU%XVWR3&,,QWHUUXSW$FNQRZOHGJH&\FOH5HJLVWHU

[% 3%B(55&6 3URFHVVRU%XV(UURU&RQWURODQG6WDWXV5HJLVWHU

[% 3%B$(55 3URFHVVRU%XV$GGUHVV(UURU/RJ5HJLVWHU

[& 3%B0,6&B&65 3URFHVVRU%XV0LVFHOODQHRXV&RQWURODQG6WDWXV5HJLVWHU

[' 3%B$5%B&75/ 3URFHVVRU%XV$UELWHU&RQWURO5HJLVWHU

Table 1-16. PowerSpan PCI Registers (cont)

Offset Register Description