Chapter 1: Hardware Description

4538 Hardware Reference Manual 13

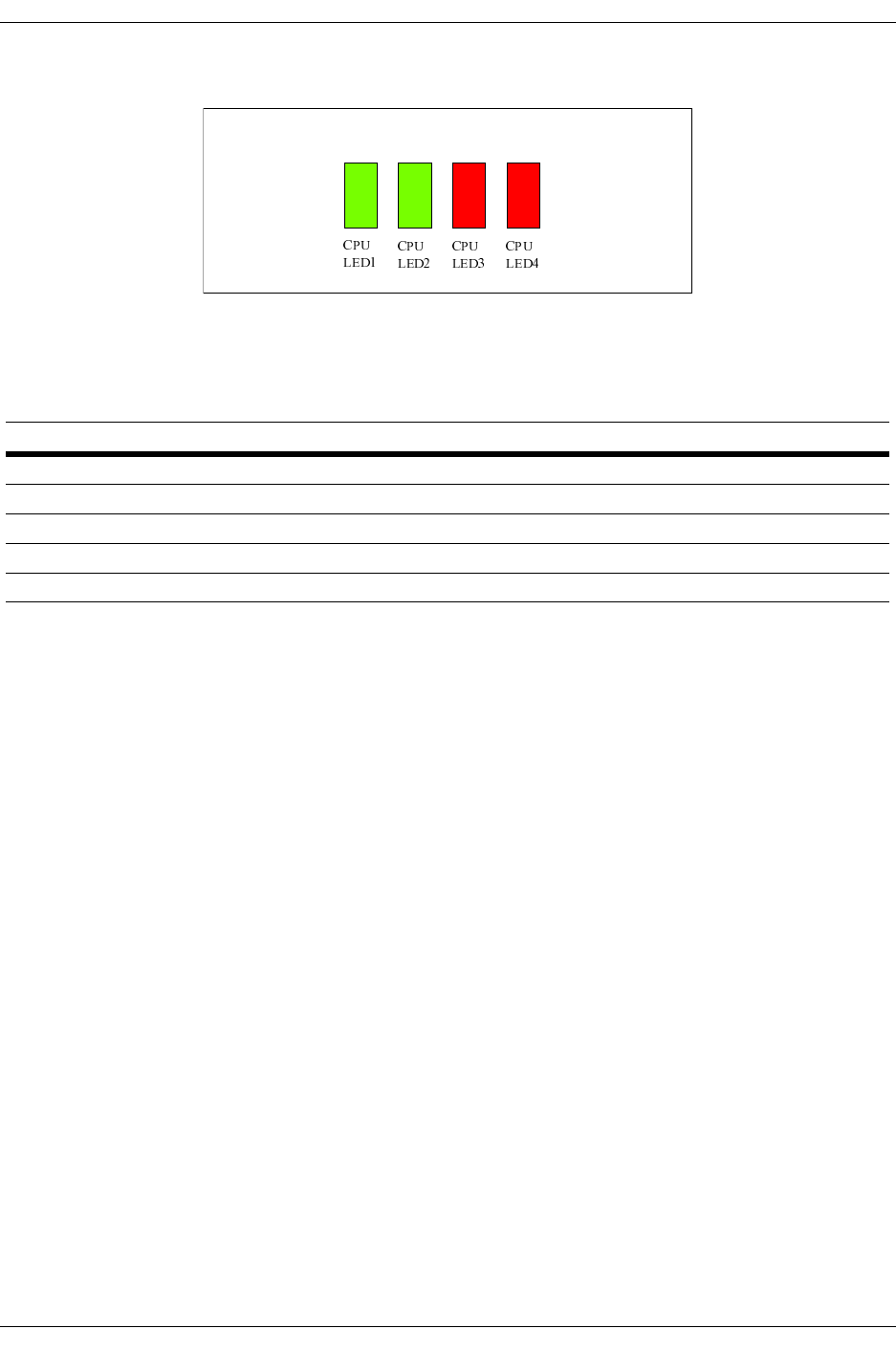

Figure 1-3. Board CPU_LEDs

The PCI Bridge

A dedicated PCI bridge, the Tundra PowerSpan, controls the interface between the card and

the host 32-bit PCI bus.

The PowerSpan implements all the registers needed by the PCI 2.2 standard, providing the

Plug-and-Play capability, as well as the Hot-Swap Friendly capabilities. It supports Target

and Master accesses between the PCI bus and the local 60x bus.

It also implements windows and different mechanisms to interface between the PCI host

and the card. Exchanges can use the following elements from the PowerSpan:

• Runtime registers (mailboxes, doorbells, semaphores)

• Four memory windows from the PCI memory space to the Local memory space

• Eight memory windows from the Local space to the PCI memory or I/O space

• Four independent bidirectional DMA engines

• An I²O messaging unit

This chip implements FIFO buffers for all the exchanges through the different windows

between the two buses, so that the local bus clock is independent from the PCI bus clock.

All the PowerSpan internal registers are grouped in a 4 KB memory space that can be

accessed by the PCI host and the local processor. On the PCI side, the PCI base address of

this register space is defined by PCI configuration register PCIBAR1 (offset 0x14). On the

local side, the local base address has been conventionally fixed to 0xF0020000.

Table 1-14. User-Programmable LED Control Ports

&30,2 6LJQDO1DPH 'HVFULSWLRQ

3' &38B/(' %RDUGXVHUSURJUDPPDEOHJUHHQ/('&38/('FRQWURO 2Q 2II

3' &38B/(' %RDUGXVHUSURJUDPPDEOHJUHHQ/('&38/('FRQWURO 2Q 2II

3' &38B/(' )URQWSDQHOXVHUSURJUDPPDEOHJUHHQ/('/('FRQWURO 2Q 2II

3' &38B/(' %RDUGXVHUSURJUDPPDEOHUHG/('&38/('FRQWURO 2Q 2II

3' &38B/(' %RDUGXVHUSURJUDPPDEOHUHG/('&38/('FRQWURO 2Q 2II

*55*