Chapter 4: Accessing the 4538 on the PCI Side

4538 Hardware Reference Manual 89

Local to PCI Interrupt (–INTA)

The PowerQUICC II can generate an interrupt toward the PCI Host by setting a doorbell

bit. Conventionally, doorbell bit 0 has been dedicated to this task, and has been associated

with PCI interrupt pin –INTA in the PowerSpan Interrupt Map registers.

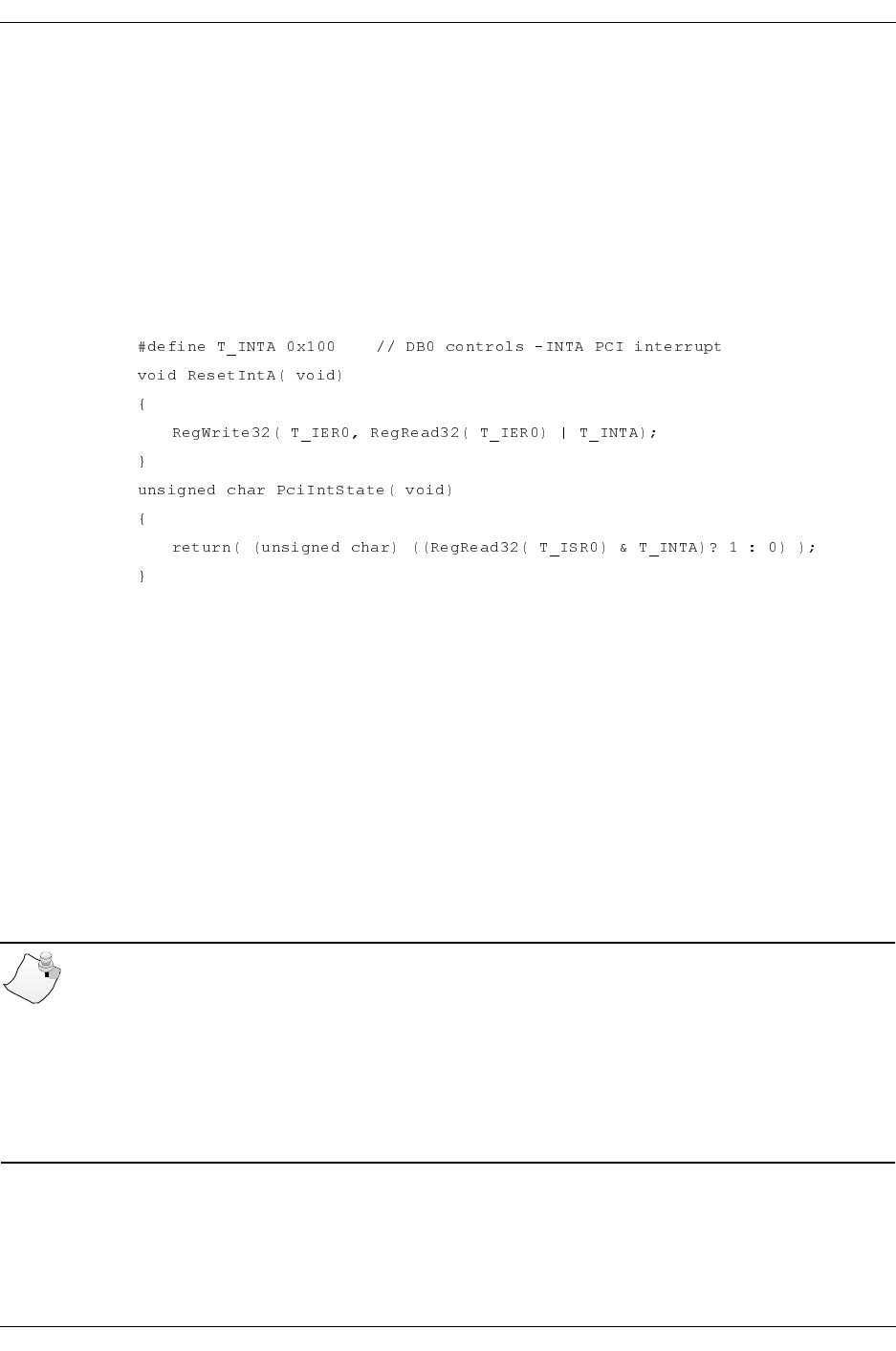

Example 4-3 is an example of C code routines to reset the PCI-to-Local interrupt and to read

the status of this interrupt from the local side.

Example 4-3. Routines Related to Local-to-PCI Interrupt

Local Space Access From PCI Memory Space

The PowerSpan provides four memory windows from the PCI memory space to the Local

memory space. In the 4538 design, the default setting in the PowerSpan serial EEPROM

enables two windows. The first one is set with a size of 2 MB and is intended for

“operational” exchanges. The second one is set with a size of 512 KB and is intended to be

used for “dumps”.

During a PCI host access to local space, the high-order address bits of the local bus must

be generated by the PowerSpan (as defined in the PowerSpan P1_TI0_ADDR register), the

low-order address bits of the local bus come from the PCI address. This mode is called

“Address Translation” in the PowerSpan manual.

NOTE

When accessing through a PowerSpan PCI-to-local window, this window must have

been enabled in the I

2

C serial EEPROM, in order to allow the PCI host to detect it at

system power-on or after hot insertion of the board, and map it in the PCI space. The

corresponding PowerSpan register “PCI Target Image Control Register” must also

have been initialized with the “Image Enable” bit set (IMG_EN=1) and the address

translation mechanism enabled (TA_EN=1).