Chapter 1: Hardware Description

4538 Hardware Reference Manual 5

local processor can also be cachable. The peripherals cannot be cachable. The area of

SDRAM memory used for the transfer of data cannot be cachable either, because it can be

modified by elements other than the PowerQUICC II, such as the PowerSpan DMA.

In order to simultaneously support cachable and non cachable areas in the SDRAM

memories, they are mapped twice in the local space. One mapping area will be defined as

cachable and the other will be defined as non cachable.

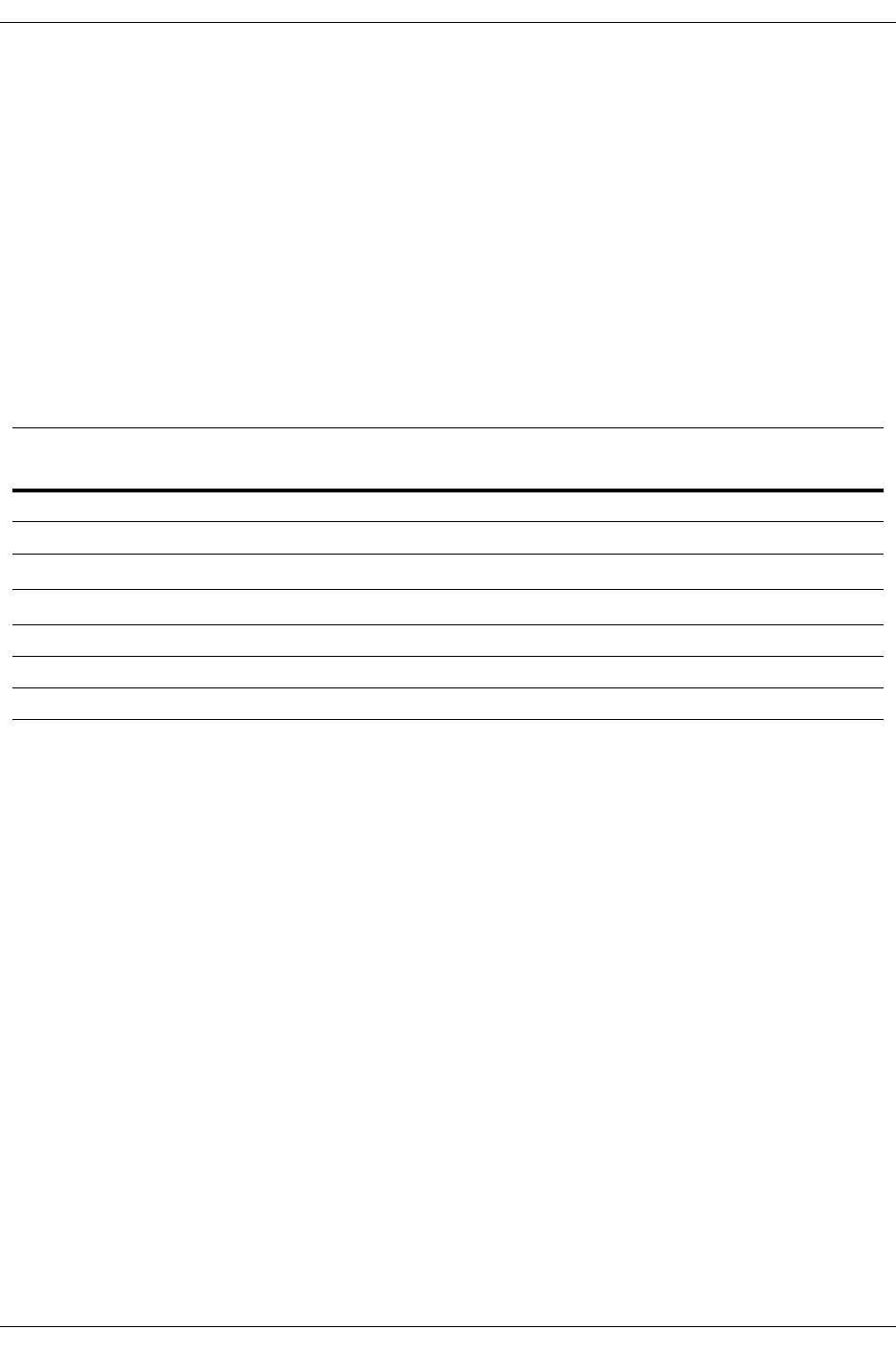

Table 1-1 and Figure 1-2 indicate the organization of the local space as defined in the

current 4538 Boot Firmware code, with the instruction and data BAT blocks and CS banks

used.

Table 1-1. PCI Local Space Mapping

Address Area Size Element Accessed

IBAT/

DBAT

CS

Bank Property

[±[)))))) 0% [EXV0DLQPHPRU\ &DFKDEOH

[

±[)))))) 0% [EXV0DLQPHPRU\GXSOLFDWHG ± 1RWFDFKDEOH

[&±[&))))))) 0% /RFDOWR3&,ZLQGRZV ±

±

1RWFDFKDEOH

[)

±[))))) .% 3RZHU6SDQLQWHUQDOUHJLVWHUV ±

±

1RWFDFKDEOH

[)

±[))))) .% 4XDG)$/& ± 1RWFDFKDEOH

[))±[)))))) .% 03&LQWHUQDOUHJLVWHUV,005LQLWLDOYDOXH ± ± 1RWFDFKDEOH

[))

±[)))))))) 0% )/$6+LQLWLDOYHFWRUWDEOHDW[))) &DFKDEOH