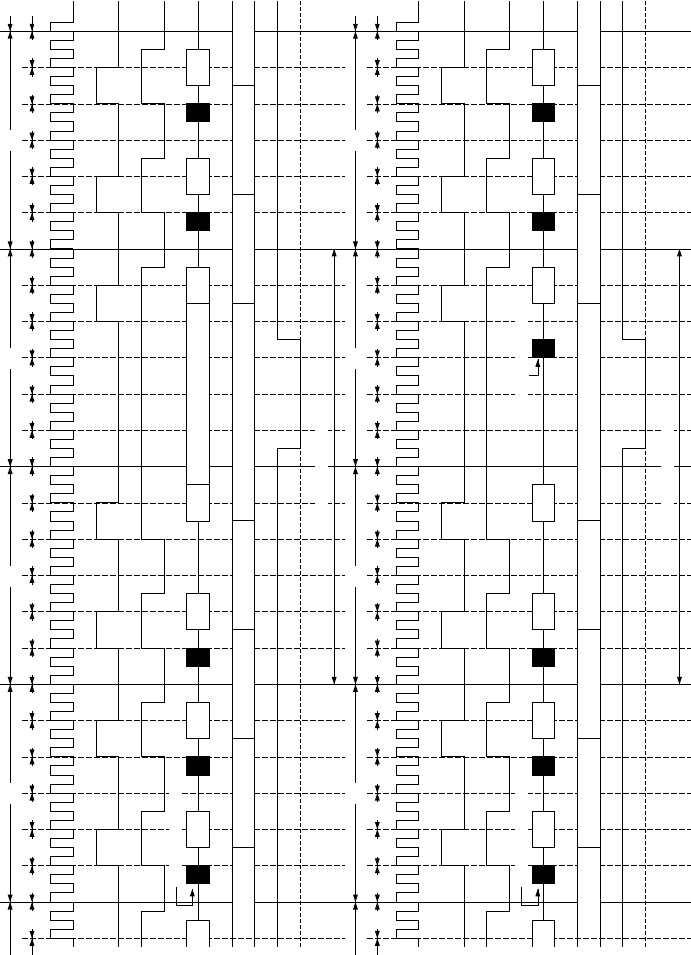

MSM80C154S/83C154S/85C154HVS

40

S1 S2 S3 S4 S5 S6

M1

S1 S2 S3 S4 S5 S6

M1

S1 S2 S3 S4 S5 S6

M2

S1 S2 S3 S4 S5 S6

M1

PCL PCL PCL PCL PCL PCLACC DATARr

INSTRUCTION IN

PCH PCH PCH PCH PORT 2 LATCH DATA PCH PCH PCH

XTAL1

1

0

ALE

1

0

PSEN

1

0

WR

1

0

PORT–0

1

0

PORT–2

1

0

S6

PCL

MOVX @Rr, A

S1 S2 S3 S4 S5 S6

M1

S1 S2 S3 S4 S5 S6

M1

S1 S2 S3 S4 S5 S6

M2

S1 S2 S3 S4 S5 S6

M1

PCL PCL PCL PCL PCL PCLRr

INSTRUCTION IN

PCH PCH PCH PCH PORT 2 LATCH DATA PCH PCH PCH

XTAL1

1

0

ALE

1

0

PSEN

1

0

RD

1

0

PORT–0

1

0

PORT–2

1

0

S6

PCL

MOVX A, @Rr

RAM DATA IN

Figure 2-29 Register R0/R1 external data memory access timing