4 www.xilinx.com XAPP169 (v1.0) November 24, 1999

1-800-255-7778

MP3 NG: A Next Generation Consumer Platform

R

The variable page size lets each mapping independently represent memory regions that can

range from 4 KB to 16 MB. This feature lets the system designer adjust the address mapping

granularity for different memory regions.

Locking TLB entries excludes entries from being recommended for replacement when there is

an address miss. This lets the system designer have mappings for critical regions of code and

or data locked into the TLB for predictable real time performance.

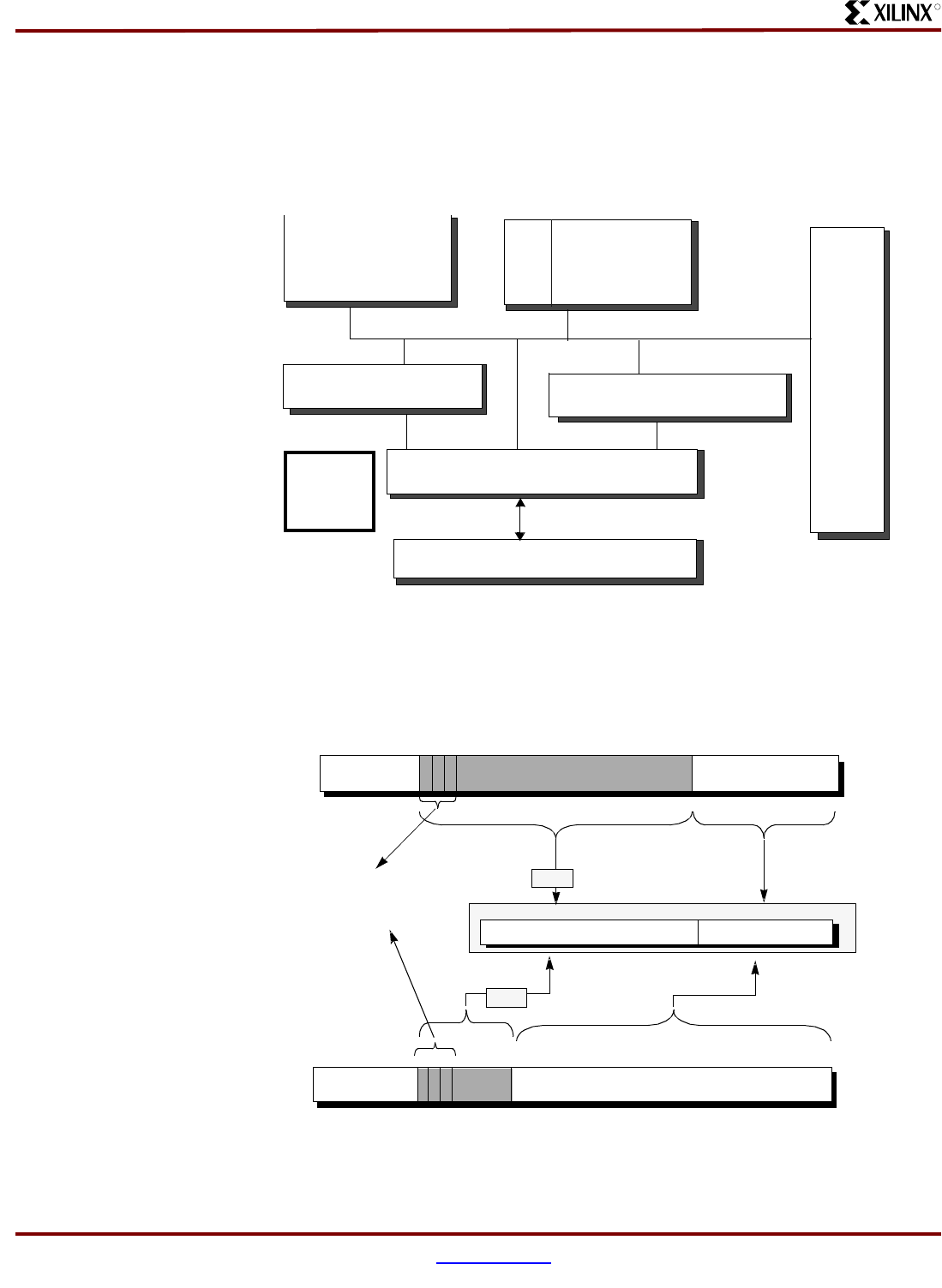

System Control

Coprocessor (CPO)

2kB D-Cache, 2-set,

Clock

Enhanced JTAG (ICE Interface)

TLB

MMU

lockable, write-back/write-through

Generation

Unit

RC32364 Bus Interface Unit

8kB

I-Cache,

lockable

2-set,

RISCore32300 Internal Bus Interface

RISCore4000 Compatible

w/

RISCore32300

TM

Extended MIPS 32

Integer CPU Core

Figure 2: RC32364 Block Diagram

(

Courtesy IDT)

28 11 0

20 12

2931

VPN

Offset

3239

ASID

8

Virtual Address with 1M (2

20

) 4-Kbyte pages

23

0

8 24

Offset

39

Virtual Address with 256 (2

8

)16-Mbyte pages

8 bits = 256 pages

20 bits = 1M

12

ASID

8

28 293132

VPN

24

Virtual-to-

physical transla-

tion in TLB

Bits 31, 30 and 29 of the

virtual address select user, super-

visor, or kernel address spaces.

Offset passed

unchanged to

physical memory

Virtual-to-physical-

translation in TLB

TLB

TLB

31 0

PFN

Offset

32-bit Physical Address

Offset pa ssed

unchanged to physical

memory.

Figure 3: RC32364 Address Translation

(Courtesy IDT)