16 www.xilinx.com XAPP169 (v1.0) November 24, 1999

1-800-255-7778

MP3 NG: A Next Generation Consumer Platform

R

CPU Interface

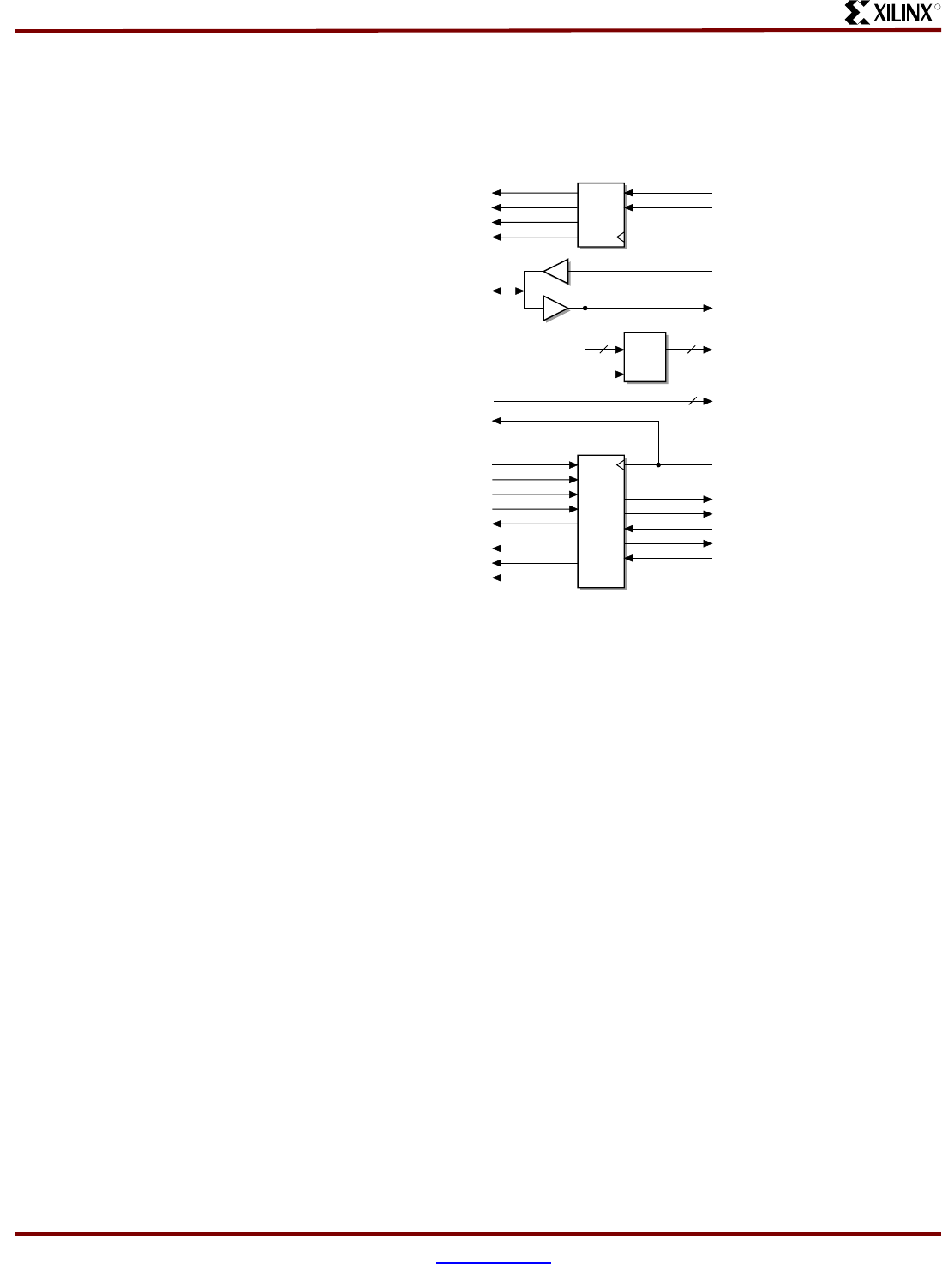

The CPU Interface block performs three functions: protocol conversion, CPU initialization and

address de-multiplexing. Figure 16 shows a block diagram of this block.

The CPU initialization block generates the required timing for the reset signals and drives

configuration information onto bus grant and the interrupts. This configuration information

configures the boot PROM width and enables the CPU timer. After initialization is complete the

block drives the IRDA and audio DAC interrupts out onto the CPU interrupt signals.

The bus state machine converts the signaling on the CPU bus into the format used on the local

IP bus, or if the transaction is to the USB interface, the signaling accepted by the USBN9602.

The FPGA device resources used to implement this block include an estimated 46 CLBs and

the 54 I/O pads listed in Table 1.

Latch

28

Enable

28

DQ

AOUT[31:4]

GNT_IN

RD_OUT_N

WR_OUT_N[3:0]

ACK_IN

REQ_OUT

Bus State

Machine

CPU_CIP_N

CPU_BE_N[3:0]

CPU_ACK_N

CPU_RD_N

CPU_AD[31:0]

CPU_ADDR[3:2]

2

AOUT[3:2]

DIN[31:0]

DOUT[31:0]

CPU_ALE

IR_INT_N

CPU

Initialization

SYS_CLK

CPU_COLDRESET_N

CPU_RESET_N

CPU_BUSGNT_N

CPU_INT_N[3:0]

DAC_INT_N

SYS_CLK

CPU_WR_N

CPU_MASTERCLK

USB_CS_N

USB_RD_N

USB_WR_N

Figure 16: CPU Interface Block Diagram