MSM80C154S/83C154S/85C154HVS

90

4.5.2.5.7 Caution about use of timer counters 0 and 1

Since the internal clock stops operation during soft power down mode (PD), the auto-reload

operation is not executed if timer/counters 0 and 1 are set to mode 2 or mode 3.

If the power down mode is to be cancelled by the timer, timer/counters 0 and 1 must be set

to mode 0 or mode 1.

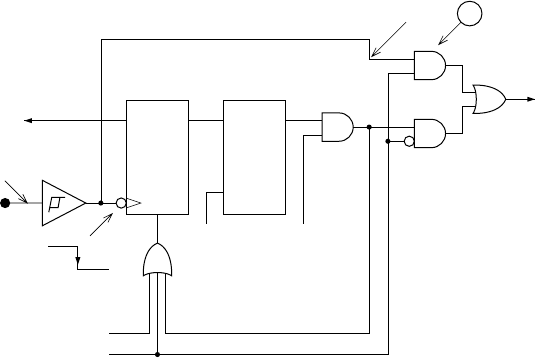

When timers 0 and 1 are set to external clock mode, the external clock is taken in as shown

in Figure 4-19 and the power down mode can be cancelled through the overflow of the timer.

If the external interrupt occurs when the T0 or T1 pin goes to “1” level and the soft power down

mode (PD) is cancelled, the gate output (A) changes from “1” level to “0” level and the counter

is incremented by 1.

In addition, “Q” of F/F1 is set on the trailing edge of T0 or T1.

Thus, the counter is incremented by additional 1.

The same event occurs not only by the external interrupt but also by the overflow of the timer.

This is because the overflow signal of the timer is made up of the timer count value “FF” and

the clock input signal “AND”. Therefore, the timer interrupt occurs when the T0 or T1 pin goes

to “1” level, and the power down mode is cancelled and the counter is incremented by

additional 1.

In cancelling the soft power down mode with the external interrupt, if the timer is set to external

clock mode, the T0 or T1 pin must be set to “0” level. If the T0 or T1 pin is at “1” level or if the

power down mode is cancelled by the overflow of the timer, the timer must be reset or the

counter must be decremented by 1.

S3

QD

L

QD

R

F/F1 F/F2

S5

T0 or T1

V

CC

RESET

PD

TIMER 0

or

TIMER 1

F/F1 F/F2

A

"1"

"1"

Figure 4-19 T0, T1 external clock detector circuit