MZ-S1

3333

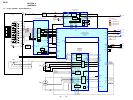

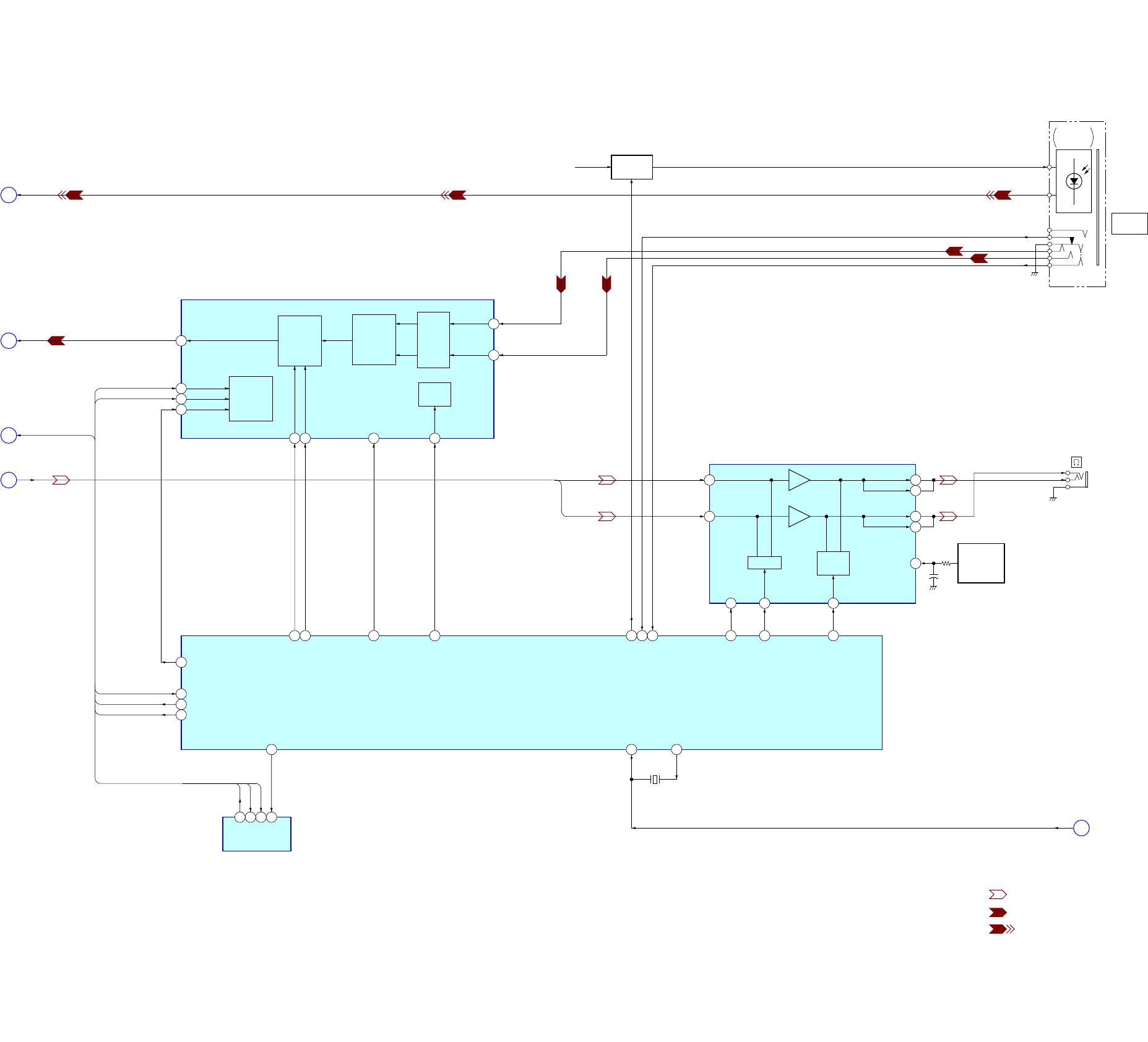

6-2. BLOCK DIAGRAM – AUDIO Section –

(LINE IN JACK)

OPTICAL

RECEIVER

J304

J301

LINE IN

(OPTICAL)

• SIGNAL PATH

: PLAYBACK

: REC (ANALOG IN)

: REC (DIGITAL IN)

2

24

4

23

22

21

15 17

49 69 93

XHP

STBY

3758 36198

151

197

45

46

47

1

71

234

B+ SWITCH

Q302

VIF B+

MUTING

HP/LINE

SWITCH

HEADPHONE AMP

IC302

OUT L

OUT R

OUTB BEEP

OUTA BEEP

IN L

IN R

HP/L

MUTE

BEEP

BEEP

MUTE

XJAC DET

XOPT CTL

FS256

XBCK

OSCO

OSCI

XCS NV1

SDI0

SCK0

SDO0

OPT DET

SYSTEM CONTROLLER,

DIGITAL SIGNAL PROCESSOR,

16M BIT D-RAM

IC801 (2/3)

150

X801

45.1584MHz

SI0

SO0

SCK0

SDI0

SDO0

SCK0

SCK0

SDO0

AOUTL,

AOUTR

ADDT

DIN1

SDO0, SCK0

XCS

SK

DI

DO

B

A

C

E

EEPROM

IC804

4

3

10

15

14

13

9

GAIN

AMP

CLOCK

DIVIDER

AUDIO

I/F

CONTROL

CONTROL

REGISTER

I/F

A/D

CONVERTER

&

HPF

RIN2

LIN2

A/D CONVERTER

IC301

SDTO

CCLK

CSN

CDTI

12

LRCK

BCLK

16

PDN

11

MCLK

196

LRCK

148

XPD ADC

147 XCS ADC

AOUTL

AOUTR

18

13

REFERENCE

VOLTAGE

SWITCHING

Q301

VREF IN

+

(Page 32)

(Page 32)

(Page 34)

(Page 32)

F

BATT

−

(Page 34)